---

ФЕДЕРАЛЬНОЕ АГЕНТСТВО

ПО ТЕХНИЧЕСКОМУ РЕГУЛИРОВАНИЮ И МЕТРОЛОГИИ

---

НАЦИОНАЛЬНЫЙ

СТАНДАРТ

РОССИЙСКОЙ

ФЕДЕРАЦИИ

ГОСТ Р

57421—

2017

---

**СИСТЕМА ТЕСТОВЫХ ПРОГРАММ

ДЛЯ ЦИФРОВЫХ ЭЛЕКТРОННЫХ МОДУЛЕЙ**

**Автоматизированные методы построения**

Издание официальное

Москва

Стандартинформ

2018

## Предисловие

- 1 РАЗРАБОТАН Открытым акционерным обществом «Авангард» (ОАО «Авангард»)

- 2 ВНЕСЕН Техническим комитетом по стандартизации ТК 420 «Базовые несущие конструкции, печатные платы, сборка и монтаж электронных модулей»

- 3 УТВЕРЖДЕН И ВВЕДЕН В ДЕЙСТВИЕ Приказом Федерального агентства по техническому регулированию и метрологии от 16 марта 2017 г. № 142-ст

- 4 ВВЕДЕН ВПЕРВЫЕ

- 5 ПЕРЕИЗДАНИЕ. Ноябрь 2018 г.

Правила применения настоящего стандарта установлены в статье 26 Федерального закона от 29 июня 2015 г. № 162-ФЗ «О стандартизации в Российской Федерации». Информация об изменениях к настоящему стандарту публикуется в ежегодном (по состоянию на 1 января текущего года) информационном указателе «Национальные стандарты», а официальный текст изменений и поправок — в ежемесячном информационном указателе «Национальные стандарты». В случае пересмотра (замены) или отмены настоящего стандарта соответствующее уведомление будет опубликовано в ближайшем выпуске ежемесячного информационного указателя «Национальные стандарты». Соответствующая информация, уведомление и тексты размещаются также в информационной системе общего пользования — на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет ([www.gost.ru](http://www.gost.ru))

© Стандартинформ, оформление, 2017, 2018

Настоящий стандарт не может быть полностью или частично воспроизведен, тиражирован и распространен в качестве официального издания без разрешения Федерального агентства по техническому регулированию и метрологии

## СИСТЕМА ТЕСТОВЫХ ПРОГРАММ ДЛЯ ЦИФРОВЫХ ЭЛЕКТРОННЫХ МОДУЛЕЙ

## Автоматизированные методы построения

System of test programs for digital electronic modules.

Automated methods of construction

Дата введения — 2017—07—01

**1 Область применения**

Настоящий стандарт распространяется на цифровые электронные модули (далее — ЦЭМ), построенные на цифровых интегральных микросхемах.

Настоящий стандарт устанавливает методы автоматизированного построения и отладки тестовых программ для автоматизированного контроля ЦЭМ на автоматизированном тестовом оборудовании — АТО.

**2 Нормативные ссылки**

В настоящем стандарте использованы нормативные ссылки на следующие стандарты:

ГОСТ 19919 Контроль автоматизированный технического состояния изделий авиационной техники. Термины и определения

ГОСТ 20911 Техническая диагностика. Термины и определения

**Примечание** — При пользовании настоящим стандартом целесообразно проверить действие ссылочных стандартов в информационной системе общего пользования — на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет или по ежегодному информационному указателю «Национальные стандарты», который опубликован по состоянию на 1 января текущего года, и по выпускам ежемесячного информационного указателя «Национальные стандарты» за текущий год. Если заменен ссылочный стандарт, на который дана недатированная ссылка, то рекомендуется использовать действующую версию этого стандарта с учетом всех внесенных в данную версию изменений. Если заменен ссылочный стандарт, на который дана датированная ссылка, то рекомендуется использовать версию этого стандарта с указанным выше годом утверждения (принятия). Если после утверждения настоящего стандарта в ссылочный стандарт, на который дана датированная ссылка, внесено изменение, затрагивающее положение, на которое дана ссылка, то это положение рекомендуется применять без учета данного изменения. Если ссылочный стандарт отменен без замены, то положение, в котором дана ссылка на него, рекомендуется применять в части, не затрагивающей эту ссылку.

**3 Термины и определения**

В настоящем стандарте применены термины по ГОСТ 19919 и ГОСТ 20911, а также следующие термины с соответствующими определениями:

3.1 **автоматизированное тестовое оборудование**: Стендовое оборудование, предназначенное для контроля функционирования и диагностики радиоэлектронной аппаратуры.

3.2 **тестовая программа**: Программа, по которой выполняется автоматизированный контроль ЦЭМ.

3.3 **логический контроль электронного модуля**: Диагностирование неисправностей логического типа фиксированный «0» или «1» на выходах логических элементов ЦЭМ.

**3.4 поведенческая модель:** Имитационная модель изделия, описывающая функционирование (поведение) изделия.

**3.5 система автоматизированного проектирования тестов (САПР тестов):** Система автоматизированного проектирования тестов для цифровых объектов диагностирования.

**3.6 скрипт:** Программа, автоматизирующая процесс генерации тестовых воздействий для объекта диагностирования.

**3.7 z-состояние:** Состояние контакта логической схемы, при котором сопротивление между этим контактом и остальной схемой очень велико и этот контакт можно считать отключенным от логической схемы.

## 4 Сокращения

В настоящем стандарте приняты следующие обозначения и сокращения:

ATO — автоматизированное тестовое оборудование;

ИМС — интегральная микросхема;

ПЛИС — программируемая логическая интегральная схема;

ПЭВМ — персональная электронная вычислительная машина;

ОД — объект диагностирования;

САПР — система автоматизированного проектирования;

ЦЭМ — цифровой электронный модуль;

Лог. «1» («0») — логическая единица (ноль);

HDL — язык описания аппаратуры (Hardware Description language).

## 5 Основные положения

**5.1** АТО должно обеспечивать:

- программную коммутацию его каналов в соответствии с расположением входов-выходов на электрических соединителях контролируемого ЦЭМ;

- автоматическую подачу на входы ЦЭМ наборов входных воздействий тестовой программы;

- автоматический анализ логических сигналов, снимаемых с выходов контролируемого ЦЭМ, в каждом наборе тестовой программы;

- автоматическую блокировку каналов, не подлежащих анализу на данном наборе;

- автоматическую выдачу информации для оценки результатов контроля.

**5.2** Тестовая программа представляет собой последовательность входных сигналов и соответствующих им выходных сигналов, обеспечивающих контроль исправности цифрового модуля, узла или устройства.

**5.3** Тестовая программа составляется для цифрового модуля конкретного типа.

**5.4** Ввод тестовой программы должен осуществляться с ПЭВМ, подключенной к АТО. Информация о прохождении тестовой программы должна выводиться на монитор ПЭВМ.

**5.5** Тестовая программа ЦЭМ должна обеспечивать его логический контроль.

**5.6** Проверки с помощью тестовой программы следует включать в методики проверки ТУ на соответствующий ЦЭМ.

## 6 Методы построения тестовых программ для цифровых электронных модулей

### 6.1 Процедура тестового контроля

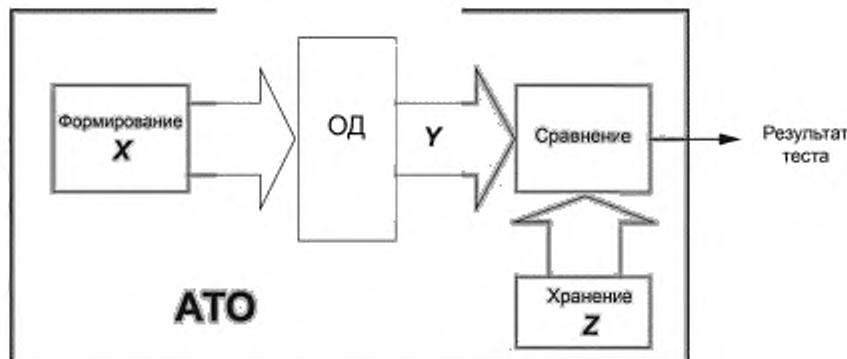

Процедура тестового контроля ЦЭМ (тестирования), выполняемая АТО, должна осуществляться в следующей последовательности:

а) подача на входы ЦЭМ, являющегося ОД, последовательности (множество  $X$ ) из  $n$  тестовых воздействий (тестовых векторов)  $X_i$ , при этом каждый вектор содержит  $k$  двоичных элементов  $x_{ij}$ :

$$X = (X_1, X_2, \dots, X_n), \quad (1)$$

где  $X_i = (x_{i1}, x_{i2}, \dots, x_{ik})$ ,

б) считывание с выходов ОД последовательности (множество  $Y$ ) *n* фактических ответов (реакций)  $Y_i$ , каждый из которых содержит  $b$  двоичных элементов:

$$Y = (Y_1, Y_2, \dots, Y_n), \quad (2)$$

где  $Y_i = (y_{i1}, y_{i2}, \dots, y_{ib})$ ;

в) сравнение  $n$  реакций  $Y_i$  с  $n$  эталонными откликами  $Z_i$  из множества  $Z$ :

$$Z = (Z_1, Z_2, \dots, Z_n), \quad (3)$$

где  $Z_i = (z_{i1}, z_{i2}, \dots, z_{ib})$ .

Схема использования АТО представлена на рисунке 1.

Примечание — Множество  $(X, Z)$  представляет собой тест конкретного ОД.

Рисунок 1 — Схема использования АТО для тестирования ОД

ЦЭМ как ОД следует представлять как набор взаимосвязанных цифровых элементов (ИМС, ПЛИС, микропроцессоров и т. д.), каждый из которых функционирует по собственному алгоритму. Для восстановления работоспособности ОД координаты любой неисправности требуется определять с точностью до корпусов цифровых элементов ОД, которые в этом случае подлежат замене.

При составлении теста ОД необходимо учитывать следующие допущения:

- модуль разработан в полном соответствии с его функциями, состоит только из цифровых элементов, его схемные решения не содержат ошибок, в том числе связанных с времennymi задержками элементов;

- модуль, изготовленный в полном соответствии с технической документацией на него и без производственного брака, считается работоспособным.

Тест должен проверять исправность элементов, входящих в состав ОД, целостность связей между элементами и отсутствие дополнительных «паразитных» связей внутри ОД. Иными словами, тест проверяет логику работы ОД.

Построение теста ОД  $(X, Z)$  должно заключаться в поиске таких последовательностей входных воздействий  $X$ , при которых порожденные ими внутренние сигналы ОД проходят со входа на выход ОД через его компоненты. В процессе этого тест должен инициировать максимально возможное количество неисправностей, которые должны проявиться на выходах ОД. Качество теста определяется долей обнаруживаемых им неисправностей.

## 6.2 Способы построения тестовых программ

6.2.1 Один из первых способов создания тестов заключается в формировании входных воздействий для ОД. Как правило, входные воздействия для ОД устанавливают таким образом, чтобы наиболее полно проверить функциональность ОД. Эти воздействия подаются на заведомо исправный ЦЭМ, а все реакции ОД  $Y$  (см. формулу 2) запоминаются (для исправных ОД  $Y = Z$ ). Из вышеупомянутых входных воздействий на ОД  $X$  (см. формулу 1) и соответствующих им реакций ОД  $Z$  (см. формулу 3) формируются тесты.

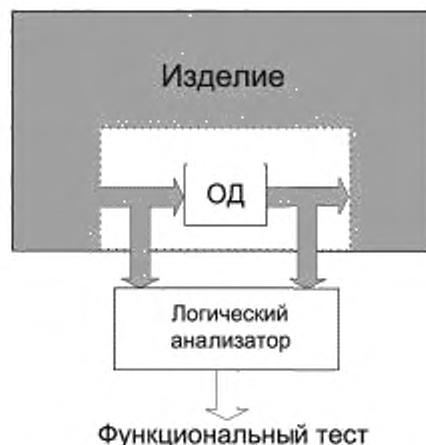

6.2.2 Тесты ОД (функциональные тесты) можно также получить путем использования логических анализаторов. При этом ЦЭМ представляется как «черный ящик» без учета его внутренней структуры и особенностей функционирования. Получаемый таким образом функциональный тест характеризуется лишь совокупностью входных воздействий  $X$  (см. формулу 1) и соответствующим ей множеством эталонных откликов  $Z$  (см. формулу 3). Вышеупомянутый функциональный тест формируется в процессе использования ОД в изделии, составной частью которого он является. В штатном режиме функционирования изделия с входов и выходов ОД снимается информация, которая и является представлением модели ОД. Схема получения функционального теста ОД представлена на рисунке 2.

Рисунок 2 — Схема получения функционального теста с помощью логического анализатора

Данный способ крайне сложен с технической точки зрения и используется крайне редко.

6.2.3 Третий способ формирования теста устройства основан на компьютерном моделировании ЦЭМ. В этом случае при создании теста вместо реального ОД используется его компьютерная модель.

При тестировании ЦЭМ достаточно локализации неисправностей на уровне корпусов компонентов ЦЭМ, так как только они подлежат замене при проведении ремонта ОД. В связи с этим для моделирования достаточно использовать поведенческие модели (HDL-модели), создаваемые с помощью языков описания аппаратуры, например Verilog или VHDL.

Наиболее предпочтительными способами создания тестов ЦЭМ являются способы, основанные на компьютерном моделировании. Это связано с тем, что моделирование, в отличие от других способов, позволяет:

- получать эталонную информацию о значениях цифровых логических сигналов в любой момент выполнения тестов;

- получать эталонные временные диаграммы цифровых сигналов в любой точке ОД;

- осуществлять предварительную оценку качества тестов.

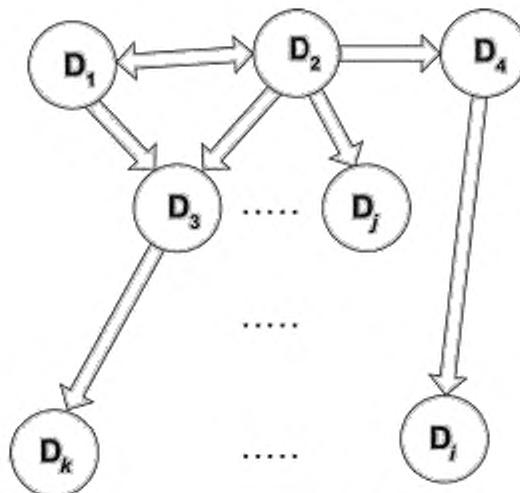

Еще одним преимуществом компьютерного моделирования является автоматическое построение HDL-моделей ОД. Оно осуществляется на основании автоматического анализа электронного представления принципиальной схемы ОД, которую можно представить в виде графа, представленного на рисунке 3.

Исходными данными для автоматического построения HDL-модели ОД являются:

- а) схема связей компонентов (Netlist), таких как процессоры, ИМС, ПЛИС, микросхемы памяти и т. д., входящих в состав ОД;

- б) HDL-модели компонентов ОД.

Для того чтобы воспользоваться преимуществами моделирования, необходимо, чтобы модель была адекватна реальному объекту. Проверка этого свойства HDL-модели ОД проводится с помощью АТО, которое позволяет сразу оценить адекватность модели ОД применительно к используемому тесту.

**Примечания**

1 Узлы графа  $D_1, D_2, \dots, D_k$  — компоненты ОД (ИМС, ПЛИС, микропроцессоров и т. д.);

2 Ребра графа — связи между компонентами.

Рисунок 3 — Представление принципиальной схемы ОД в виде графа

### 6.3 Этапы автоматизированного построения тестовых программ

#### 6.3.1 Общие положения

Автоматизированное построение тестовых программ (тестов) должно быть обеспечено программной поддержкой этого процесса САПР тестов для цифровых ОД.

*Пример — САПР «СИМ-ТЕСТ».*

Разработка тестов должна осуществляться применительно к конкретному образцу АТО. Автоматизированное построение тестовых программ (тестов) должно производиться в несколько этапов.

#### 6.3.2 Анализ объекта диагностирования

Для создания теста необходимо, насколько это возможно, в деталях знать логику работы ОД. Это связано с необходимостью учета особенностей ОД при составлении теста. Так, например, началу функционирования любого ОД в соответствии со своим предназначением, как правило, предшествует подготовительный период. При этом могут производиться сброс ОД в исходное состояние, запись определенной информации в управляющие регистры, загрузка программы из оперативной памяти в микропроцессор и т. д. После завершения подготовительного периода ОД готов к проведению тестирования.

Для получения этой информации требуются ознакомление с принципами функционирования ОД, изучение эксплуатационной и конструкторской документации, анализ схемы ОД. Выполнение задач данного этапа требует привлечения специалистов. Продолжительность этапа определяется сложностью ОД, полнотой информации о нем, качеством эксплуатационной документации и квалификацией привлекаемых специалистов.

#### 6.3.3 Формирование схемы объекта диагностирования в электронном виде

В некоторых случаях для ОД не имеется принципиальной схемы в электронном виде. В этих случаях требуется по бумажному представлению схемы воссоздавать (создавать) ее электронный вид. На данном этапе выполняется работа, требующая привлечения специалиста с навыками работы в САПР проектирования печатных плат радиоэлектронной аппаратуры, в которой описываются состав компонентов ОД и связи между ними.

При отсутствии электронного представления данный этап — это довольно трудоемкий процесс, длительность которого зависит от объема схемы, ее сложности и квалификации специалиста по САПР.

Наличие принципиальной схемы ОД в электронном виде в одном из форматов САПР проектирования печатных плат радиоэлектронной аппаратуры позволяет с помощью САПР тестов свести трудоемкость описания состава компонентов ОД и связей между ними практически к нулю.

#### 6.3.4 Исключение аналоговых элементов из электронного вида схемы объекта диагностирования

На этом этапе проводят анализ принципиальной схемы ОД на предмет наличия в нем аналоговых элементов. Для каждого из них должен быть сделан выбор о его использовании в дальнейшем в процессе автоматизированного создания тестов. В зависимости от функциональности компонента он может быть удален из схемы или заменен на соответствующий функциональный цифровой компонент. Пример такой замены приведен в приложении А.

В результате выполнения этих действий преобразованная принципиальная схема ОД будет состоять только из цифровых логических компонентов. Данные, представленные в такой электронной схеме, готовы для формирования в дальнейшем поведенческой модели функционирования ОД.

#### 6.3.5 Создание поведенческих моделей компонентов объекта диагностирования

Для создания поведенческой модели всего ОД в качестве исходных данных должна быть использована информация (см. рисунок 3), извлекаемая из электронного представления схемы ОД и поведенческих моделей компонентов, используемых в ОД.

Поведенческие модели ранее созданных компонентов должны храниться в электронной библиотеке САПР тестов. На данном этапе осуществляются создание и отладка моделей тех компонентов, данные о которых отсутствуют в библиотеке. Этот этап является чрезвычайно важным, так как именно адекватность поведенческих моделей реальным компонентам обеспечивает адекватность модели всего ОД в целом.

Создание адекватных поведенческих моделей компонентов требует привлечения высококвалифицированных специалистов. Временные затраты при этом определяются квалификацией этих специалистов как в области радиоэлектроники, так и в области моделирования. По мере накопления в электронной библиотеке САПР поведенческих моделей компонентов продолжительность данного этапа существенно уменьшается и в конечном итоге сводится к нулю.

#### 6.3.6 Создание поведенческой модели всего объекта диагностирования

На этом этапе осуществляется автоматическое создание поведенческой модели всего ОД средствами САПР тестов. Эта операция должна осуществляться с использованием поведенческих моделей компонентов, записанных в электронную библиотеку САПР, и данных о связях между ними, извлекаемых из электронной схемы ОД (см. рисунок 3).

#### 6.3.7 Формирование входных воздействий

Автоматизированное формирование входных воздействий  $X$  (см. формулу 1) для создаваемого теста может осуществляться двумя методами:

а) путем составления скрипта, определяющего правила генерации тестовых воздействий в тахах теста;

б) с помощью средств ограниченного случайного моделирования.

Реализация этих способов должна быть обеспечена поддержкой САПР тестов.

Первый из вышеупомянутых методов заключается в составлении разработчиком теста некоторой последовательности правил формирования входных воздействий. Каждое такое правило определяет порядок подачи на вход определенной последовательности сигналов  $(x_{i,j}, x_{i+1,j}, \dots, x_{k,j})$  или  $(x_{i,j}, x_{i,j+1}, \dots, x_{i,j+m})$ ,  $(x_{i+1,j}, x_{i+1,j+1}, \dots, x_{i+1,j+m})$ , ...,  $(x_{k,j}, x_{k,j+1}, \dots, x_{k,j+m})$ , где  $(x_{i,j}, x_{i+1,j}, x_{i+2,j}, \dots, x_{k,j})$  — последовательность двоичных сигналов, подаваемых на  $j$ -й вход ОД в период с  $i$ -го по  $k$ -й такт (см. формулу 1), с указанием, с какого значения (логический «0» или «1») должна начинаться последовательность, какова скважность импульсов и т. д.:

$$(x_{i,j}, x_{i,j+1}, \dots, x_{i,j+m}), (x_{i+1,j}, x_{i+1,j+1}, \dots, x_{i+1,j+m}), \dots, (x_{k,j}, x_{k,j+1}, \dots, x_{k,j+m}) —$$

последовательность двоичных сигналов, подаваемых на  $j, j+1, \dots, j+m$  входы ОД в период с  $i$ -го по  $k$ -й такт.

Второй метод предполагает формирование множества входных воздействий  $X$  случайным образом. Важной составной частью этого метода является система контроля ограничений содержимого множества  $X$ , сгенерированного случайным образом. Эта система блокирует включение в состав множества  $X$  тестовых векторов  $X_i$  (см. формулу 1), которые представляют собой запрещенные комбинации для ОД, для которого создается тест.

**6.3.8 Формирование теста**

Завершение работ по автоматизированному созданию тестов осуществляется в автоматическом режиме путем проведения моделирования функционирования ОД, осуществляемого средствами САПР тестов. При этом на вход модели (входные контакты краевых разъемов ОД) подаются ранее сформированные входные воздействия  $X$  (см. формулу 1), а с выходов модели (выходных контактов краевых разъемов ОД) снимаются реакции ОД  $Y$  (см. формулу 2), которые принимаются за эталонные  $Z$  (см. формулу 3).

Совокупность входных воздействий  $X$  и соответствующих им эталонных откликов  $Z$  образуют собой тест ( $X, Z$ ), который записывается в базу данных.

**6.3.9 Предварительная оценка качества теста**

Для принятия решения о возможности использования теста ( $X, Z$ ) на реальном ОД необходимо провести оценку его качества, которая определяется с помощью формулы

$$K = \frac{N_{\text{изм}}}{N}, \quad (4)$$

где  $N$  — число цепей в ОД;

$N_{\text{изм}}$  — число цепей из  $N$  цепей, в которых произошло хотя бы одно изменение значений логических сигналов «0» $\rightarrow$ «1» или «1» $\rightarrow$ «0».

По результатам этого анализа принимается решение о возможности использования теста на реальном ОД или о необходимости доработки теста — итерационное выполнение 6.3.7—6.3.9.

Приложение А

(справочное)

## Пример замены аналогового элемента на соответствующую функциональную цифровую модель компонента

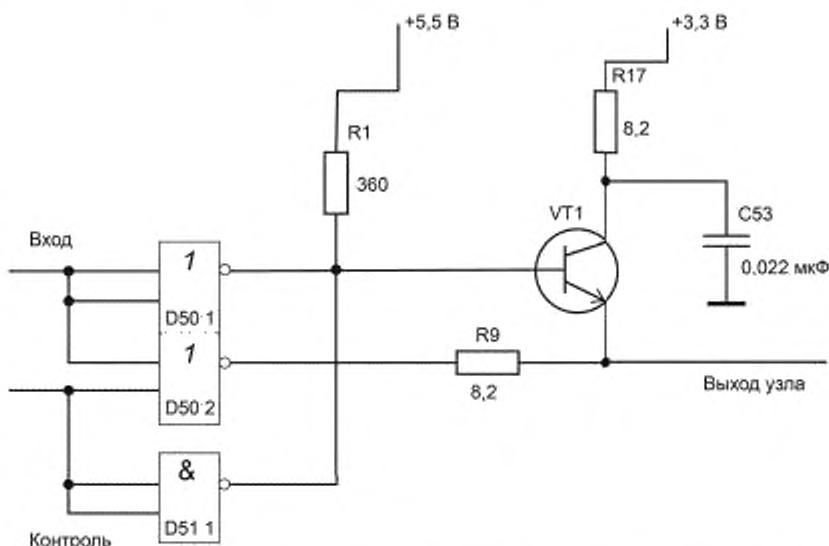

Допустим, что в анализируемом ОД используется аналоговый элемент — управляемый одноразрядный повторитель цифрового сигнала с третьим состоянием. На рисунке А.1 приведена его схемотехническая реализация, взятая из принципиальной схемы некоторого устройства.

Этот управляемый повторитель реализован на базе шинного формирователя 1102АП8 (D50), схемы И-НЕ с открытым коллектором 539ЛА9 (D51), транзистора, трех резисторов и фильтрующего конденсатора. Из анализа этого узла можно заключить, что при подаче логического нуля на управляющий вход («control») сигнал на выходе («output») узла повторяет сигнал на информационном входе («input»), правда с уменьшенным уровнем логической «1».

Рисунок А.1 — Схема управляемого одноразрядного повторителя цифрового сигнала с третьим состоянием

При подаче на управляющий вход логического сигнала «1» выход узла («output») будет находиться в z-состоянии. Функциональность этого узла на языке Verilog представляется следующим образом:

```

assign s_output = (s_control == 0) ? s_input : 1'bz;

```

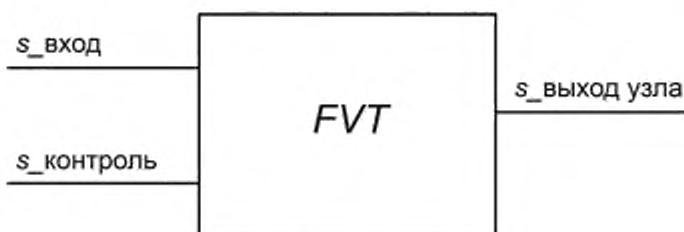

При коррекции исходной схемы ОД рассмотренный аналоговый элемент заменяется на соответствующую функциональную цифровую модель компонента *FVT*, выполняющего те же функции. Вид этого компонента приведен на рисунке А.2.

Рисунок А.2 — Компонент *FVT*

Аналогичным образом необходимо поступить со всеми другими узлами, реализующими цифровые функции с помощью аналоговых элементов. Следует отметить также, что поскольку при формировании тестов рассматривается только реакция ОД на цифровые воздействия, то все элементы, связанные с фильтрацией питания (резисторы, конденсаторы, стабилизаторы), необходимо удалить из схемы ОД.

---

УДК 681.3.023-182.77:006.354

ОКС 35.240.01

Э67

ОКП 50 1250

---

Ключевые слова: модули цифровые электронные, методы, формирование и построение тестовых программ, HDL-модели, поведенческая модель, автоматизированное тестовое оборудование

---

Редактор *Е.В. Яковлева*

Технический редактор *В.Н. Прусакова*

Корректор *Е.Р. Аронян*

Компьютерная верстка *Ю.В. Половой*

Сдано в набор 08.11.2018. Подписано в печать 28.11.2018. Формат 60 × 84<sup>1</sup>/<sub>8</sub>. Гарнитура Ариал.

Усл. печ. л. 1,40. Уч.-изд. л. 1,28.

Подготовлено на основе электронной версии, предоставленной разработчиком стандарта

---

Создано в единичном исполнении ФГУП «СТАНДАРТИНФОРМ»

для комплектования Федерального информационного фонда стандартов,

117418 Москва, Нахимовский пр-т, д. 31, к. 2.

[www.gostinfo.ru](http://www.gostinfo.ru) [info@gostinfo.ru](mailto:info@gostinfo.ru)